NAOJ GW Elog Logbook 3.2

Displaying report 1-1 of 1.

NaokiAritomi - 23:53, Monday 18 February 2019 (1222)

Error signal of coherent control

[Aritomi, Yuhang, Matteo]

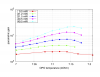

Since we found that parametric gain is not as high as before, we measured parametric gain again changing OPO temperature and green power. First attached figure shows the result. The optimal temperature of OPO is not 7.05 kOhm anymore, but it's around 7.16 kOhm. The reason why optimal OPO temperature changed is not identified yet, but temperature change in clean room could be one reason.

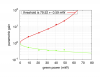

Second attached figure shows parametric gain with optimal OPO temperature. OPO threshold is now 79.52 +- 0.59 mW. It's reasonable.

With green power of 51 mW and OPO temperature of 7.16 kOhm, we made BAB and p pol overlapped inside OPO. P pol beat note was 208 MHz. The laser setting is as follows.

| Current (A) | Temperature (deg) | |

| CC | 1.183 | 38.16 |

| P pol | 1.338 | 32.5 |

Then we found a problem that we couldn't lock p pol PLL at 208 MHz with PLL setting of reference frequency 104 MHz and divider 2 (104*2=208 MHz). However, when we changed the reference frequency 69 MHz and divider 3 (69*3= 207 MHz), we can lock PLL at 207 MHz.

The reason is to be investigated.

Then we found a problem that we couldn't lock p pol PLL at 208 MHz with PLL setting of reference frequency 104 MHz and divider 2 (104*2=208 MHz). However, when we changed the reference frequency to 69 MHz and divider to 3 (69*3= 207 MHz), we can lock PLL at 207 MHz. The reason is to be investigated.

After we demodulated reflection of OPO with 14 MHz, we got the error signal for phase locking of green and CC as shown in last attached picture. Modulation of green phase was 100 Hz, 4 Vpp.

Then we found a problem that we couldn't lock p pol PLL at 208 MHz with PLL setting of reference frequency 104 MHz and divider 2 (104*2=208 MHz). However, when we changed the reference frequency 69 MHz and divider 3 (69*3= 207 MHz), we can lock PLL at 207 MHz.

The reason is to be investigated.

Images attached to this report